関連記事

東工大、世界最小のクロック回路を開発 5ナノメートル半導体プロセスで実現

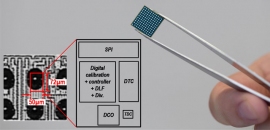

研究グループが開発した世界最小のクロック回路を搭載したチップ写真(写真:東工大の発表資料より)[写真拡大]

東京工業大学は10日、最先端の5ナノメートルの半導体プロセスでは世界初となる、世界最小のクロック回路の開発に成功したと発表した。

【こちらも】東工大、マイクロ波によるバイオマスの超急速熱分解に成功 低炭素社会実現に期待

■小型化困難なアナログ回路

大規模集積回路(LSI)は、ほとんどの携帯電話やパソコン、テレビ等の電子機器に搭載されている。LSIは、デジタル信号を処理するデジタル回路部と、外部からのアナログ信号を扱うアナログ回路部の2つから構成されている。LSIにおいてシリコンチップ上の素子数(集積度)が増加するとともに、性能が向上している。

LSIのデジタル回路部については、微細化が進んでいるという。韓国サムスン電子や台湾TSMCらは、線幅5ナノメートル(ナノは10億分の1)の半導体チップの開発に成功、小型化と高性能化が実現された。

他方アナログ回路は小型化が困難で、製造プロセスが微細化するにつれ設計が困難になるという問題を抱える。

所望の周波数をもつ信号が生成できるクロック回路がLSIに内蔵されているが、集積回路だけで正確な周波数を作れない。そのため水晶発振体を活用して所望の周波数の信号を得るPLL方式のクロック回路が用いられる。だがアナログ回路の一種であるPLLは手作業での設計を要し、設計ルールの複雑化や面積増大による性能劣化という問題を抱えていた。

■完全自動設計可能なクロック回路

東工大とソシオネクストの研究者から構成されるグループは、クロック回路を小型化するため、デジタル型のPLLに注目。デジタルPLLはこれまで、デジタル制御発振器(DCO)や時間差デジタル変換器(TDC)によって、アナログ回路構成が可能だったが、アナログ回路設計によるTDCが必要だった。

研究グループは今回、デジタル時間変換器(DTC)とTDCとを組み合わせることで、完全なデジタル回路化に成功した。PLL回路全体がデジタル回路として構成可能になったことで、通常のデジタル回路と同様に、自動設計が可能になったという。

研究の詳細は、IEEE Solid-State Circuit Lettersにて1月27日に掲載されている。(記事:角野未智・記事一覧を見る)

スポンサードリンク